8253 pin diagram YouTube

In this video, i have explained Programmable Interval Timer 8254/8253 by following outlines:0. Programmable Interval Timer 8254/82531. Basics of Programmable.

8253/54 Programmable Interval Timer YouTube

Micro44: 8253/8254 Programmable Interval Timer | 8253 Block Diagram | 8254 Block Diagram - YouTube Microprocessor Handwritten Notes (AKTU Syllabus): https://imojo.in/22m2qfi Download.

8253/8254 Programmable Interval Timer Block diagram Complete

It covers complete description of 8253 IC ( PIT) viz. pin diagram, block diagram and working modes.

CSE TUBE CS2252 / CS42 / 10144 CS403 / 80250010 / EC1257

Let us first take a look at the pin diagram of Intel 8255A −. Now let us discuss the functional description of the pins in 8255A. Data Bus Buffer. It is a tri-state 8-bit buffer, which is used to interface the microprocessor to the system data bus. Data is transmitted or received by the buffer as per the instructions by the CPU.

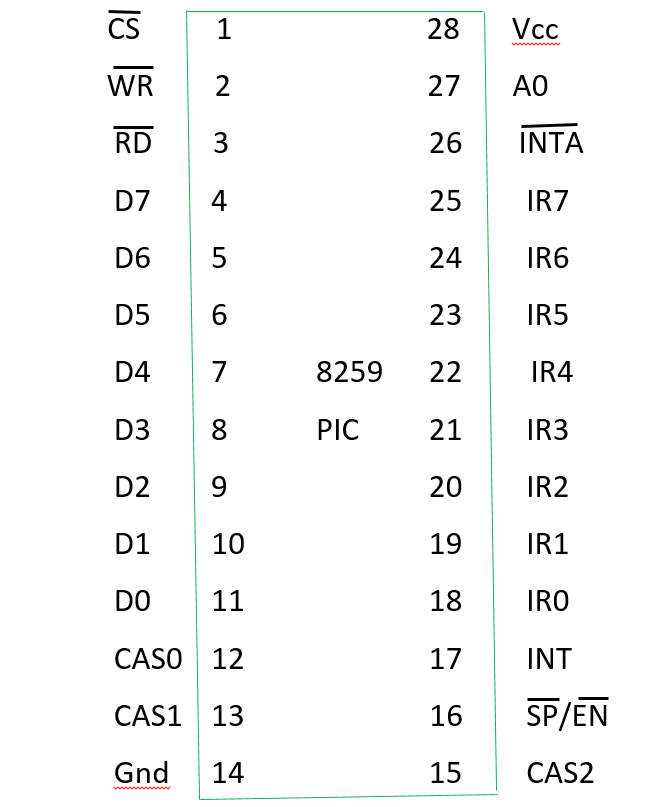

Introduction to 8259 (8259 microprocessor) Interrupt Handling Bcis

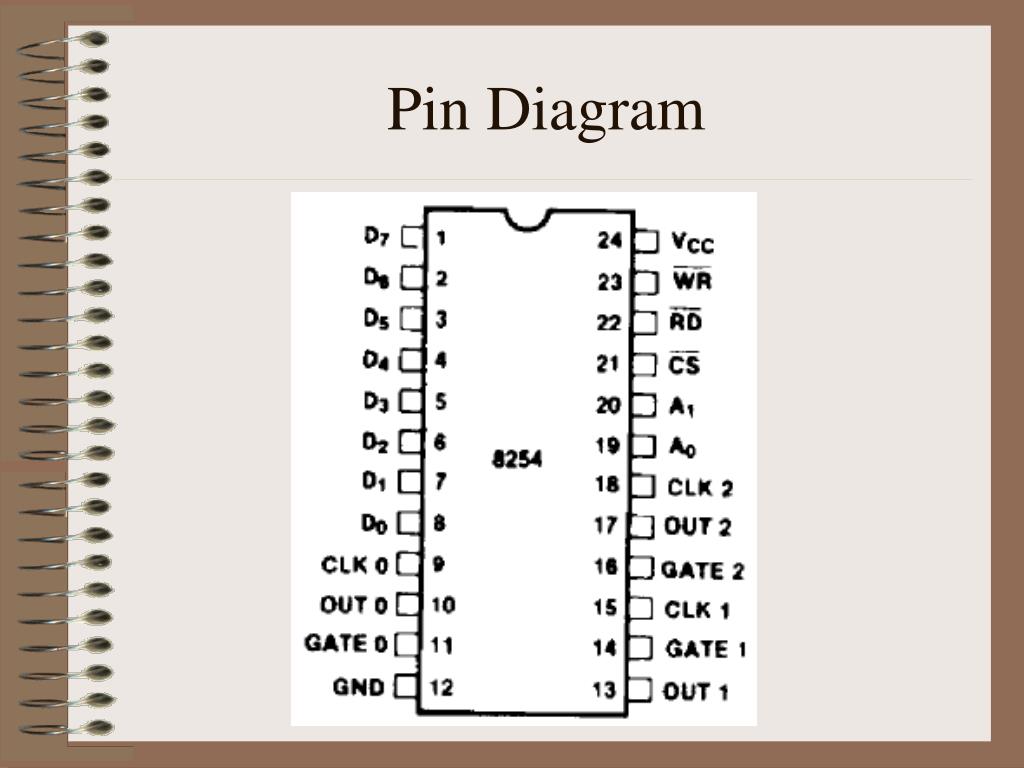

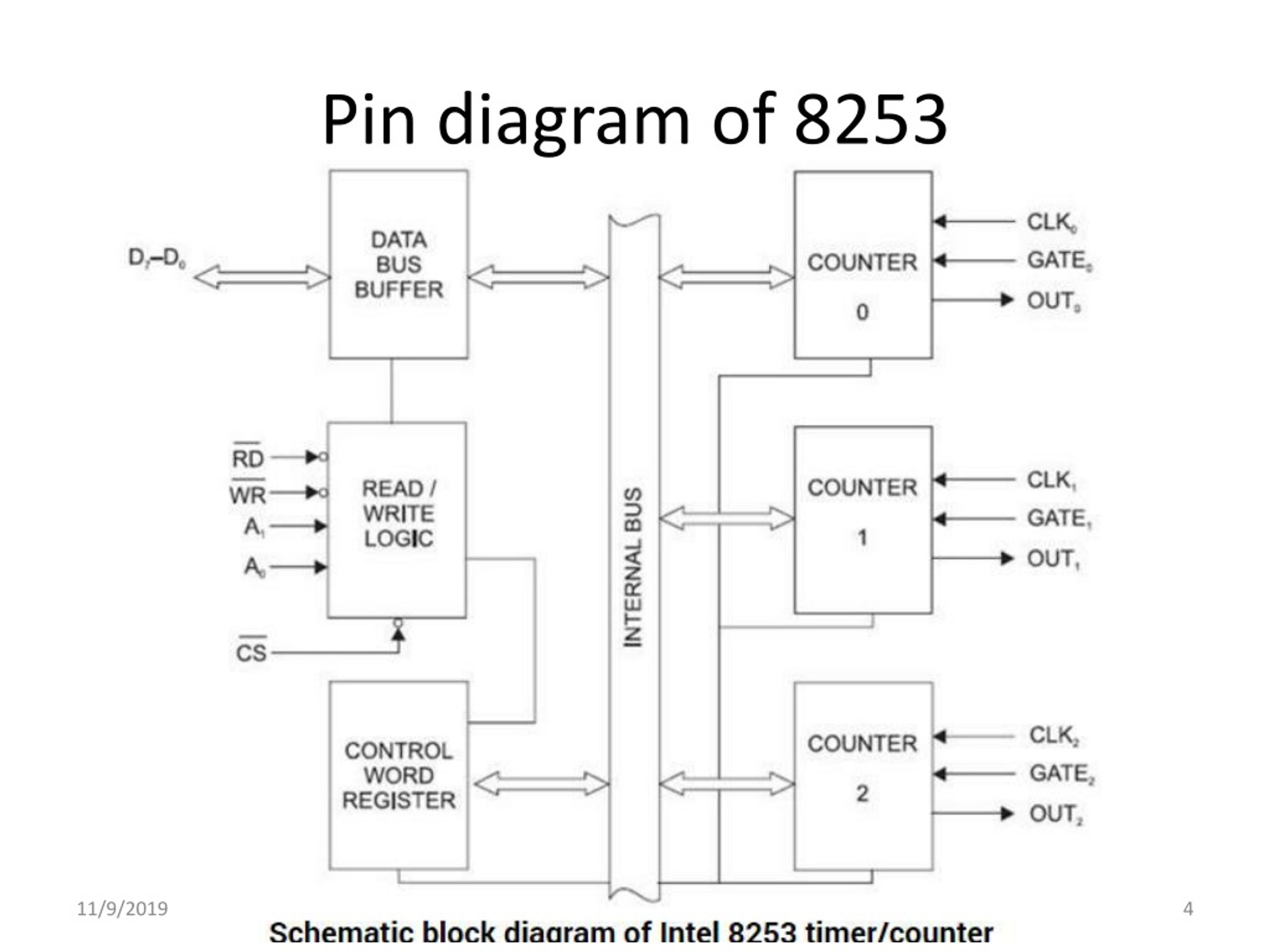

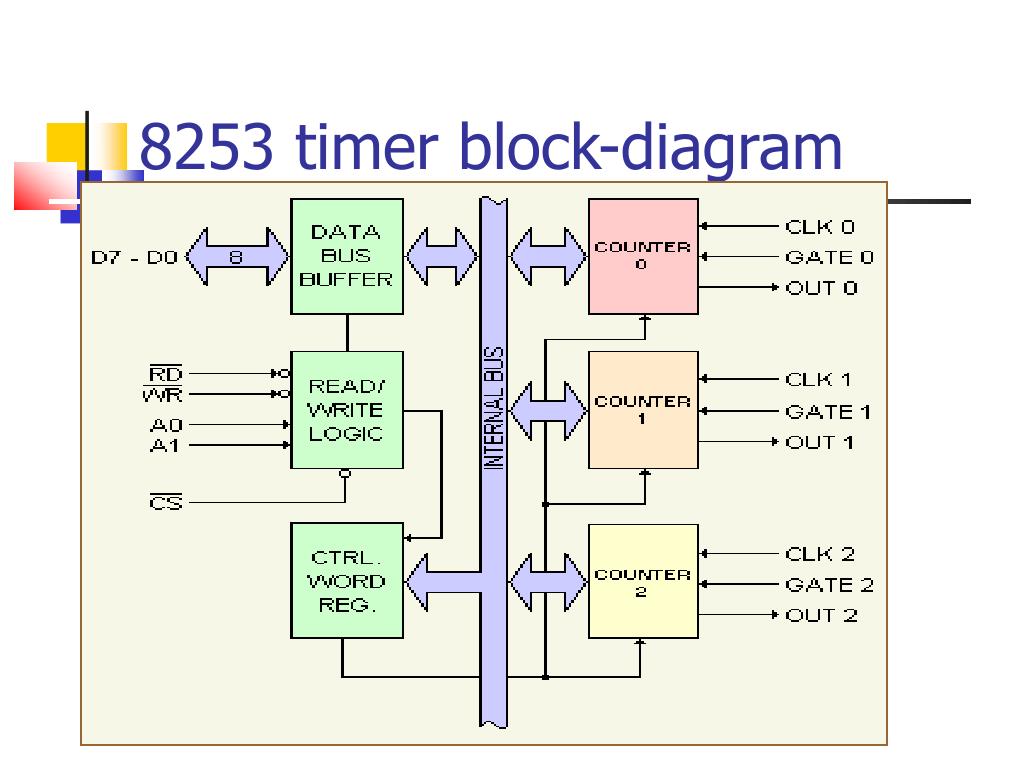

The pin diagram, block diagram of 8253, interfacing with 8085 microprocessor and operation of each mode have been explained in this section. Pin Diagram of 8253 The 8253 timer is a 24-pin IC and operates at +5 V dc. It consists of three independent programmable 16-bit counters: Counter 0, Counter 1, and Counter 2.

MSXMIDI

Intel 8254 is a programmable interval timer designed by intel is a programmable external timer device built with an aim to resolve the time control issues that occur in between various processes occurring within the microprocessor. In order to communicate with the processor, it has a total of 8 data lines.

Pin On Diagrams Gambaran

The 82C54 is pin compatible with the HMOS 8254, and is a superset of the 8253. Six programmable timer modes allow the 82C54 / 8253 to be used as an event counter, elapsed time indicator, programmable one-shot, and in many other applications. 4.4.1 Block diagram. The timer has three independent, programmable counters and they are all identical. The

8253/8254 Programmable Interval Timer Block Diagram and Pin

Block diagram of Intel 8253 The timer has three counters, numbered 0 to 2. [7] Each channel can be programmed to operate in one of six modes. Once programmed, the channels operate independently. [1] Each counter has two input pins - "CLK" ( clock input) and "GATE" - and one pin, "OUT", for data output.

Block diagram of 8253

The block diagram of 8253 Interfacing 8253 with 8085 Now let us see how to interface this 8253 timer chip with the Intel 8085 microprocessor. From the following picture, we can see that the data bus D 7-0 of 8085 is connected to the data pins D 7 to D 0 of 8253.

PPT Programmable interval timer/counter (IC 8253) PowerPoint

A "low" on this input enables the 8253. No reading or writing will occur unless the device is selected. The CS input has no effect upon the actual operation of the counters. 8253 BLOCK DIAGRAM CS RD WR Ai A0 0 1 0 0 0 Load Counter No. 0 0 1 0 0 1 Load Counter No. 1 0 1 0 1 0 Load Counter No. 2 0 1 0 1 1 Write Mode Word 0 0 1 0 0 Read.

PPT Lecture 3 PowerPoint Presentation, free download ID4572821

It has three basic functions − Programming the modes of 8253/54. Loading the count registers. Reading the count values. Read/Write Logic It includes 5 signals, i.e. RD, WR, CS, and the address lines A 0 & A 1. In the peripheral I/O mode, the RD and WR signals are connected to IOR and IOW, respectively.

Block Diagram of 8253 8254 YouTube

Block diagram of 8253 and Pin diagram of 8253 August 18, 2022 by Er. S.Pradhan In this article we are discus about the functional block diagram and pin description of 8253 or 8254 (PIT) Programmable Interval Timer. The 8253 is a programmable universal timer design for use in microcomputer system.

Write a control word for counter 1 of 8253 / 8254, Electrical Engineering

Subject - MicroprocessorVideo Name - 8253/8254 Programmable Interval Timer : Block Diagram and Pin DescriptionChapter - Study and Interfacing of Peripherals.

8253

It has three basic functions − Programming the modes of 8253/54. Loading the count registers. Reading the count values. Read/Write Logic It includes 5 signals, i.e. RD, WR, CS, and the address lines A0 & A1. In the peripheral I/O mode, the RD and WR signals are connected to IOR and IOW, respectively.

Block diagram of 8253

The 82C54 is pin compatible with the HMOS 8254, and is a superset of the 8253. Six programmable timer modes allow the 82C54 / 8253 to be used as an event counter, elapsed time indicator, programmable one-shot, and in many other applications. Block diagram

Fig. C.4 The control word and bit definitions of 8253 (PIT) Download

File:Intel 8253 block diagram.svg. Size of this PNG preview of this SVG file: 590 × 440 pixels. Other resolutions: 320 × 239 pixels | 640 × 477 pixels | 1,024 × 764 pixels | 1,280 × 955 pixels | 2,560 × 1,909 pixels. Original file (SVG file, nominally 590 × 440 pixels, file size: 29 KB) This is a file from the Wikimedia Commons.